Posts Tagged “layout”

Enquanto eu desfrutava os projetos do Concurso 7400 me ocorreu que muitos dos projetos lógicos submetidos não tinham um dos elementos de segurança mais básicos para garantir um bom resultado.

O aspecto mais desconsiderado foi a falta de capacitores de bypass. Então, após ler um artigo sobre a Lei de Murphy que referenciava um outro application note da Maxim, eu decidi escrever um pouco sobre capacitores de desacoplamento e bypass.

Como uma pessoa que pode ser considerada velha neste trabalho, eu já experimentei os problemas da ausência de desacoplamento em primera mão. Meu primeiro projeto em alta velocidade foi como aprendiz em meados dos anos oitenta em uma grande empresa de eletrônica. O projeto que eu estava construindo, um medidor de frequência digital, usava portas lógicas 74Fxx a uma velocidade de 11MHz (que era muito rápido para a época). Ele estava feito em “wire-up” em uma placa do tamanho de uma placa euro-card dupla e usava em torno de 40 CIs. Quando chegou a hora de ligar, eu notei que ele não funcionava como o esperado e todo o tipo de coisa apareceu em todos os lugares. Depois de verificar a montagem várias vezes eu conversei com o meu supervisor sobre o problema e ele me disse: “Não existem capacitores de bypass; monte-os em todos os chips, junto à alimentação, e nós conversaremos novamente”. Completamente desorientado eu fiz o que ele disse e, como um milagre, tudo simplesmente funcionou. Porque a aparente inerte capacitância da fonte de alimentação não faz as coisas simplesmente funcionarem?

Meu supervirsor então me falou sobre correntes de chaveamento/surto, indutância dos fios e sobre o conto do desacoplamento. Eu admito que somente alguns anos depois eu realmente entendi o que ele falava, mas a lição estava aprendida: sempre coloque capacitores na alimentação de CIs lógicos.

Os termos “capacitor de bypass” e “desacoplamento” não são simplesmente palavras aleatórias, elas possuem um significado específico neste contexto:

– desacoplamento (decoupling): o ato de separar (parcialmente) a fonte de energia do CI da fonte principal de alimentação.

– capacitor de bypass: o capacitor montado desta forma atua como bypass da fonte principal de alimentação e funciona (temporariamente) como uma fonte de energia local.

Mas porque isso é tão importante? Bom, deixe-me te mostrar uma imagem:

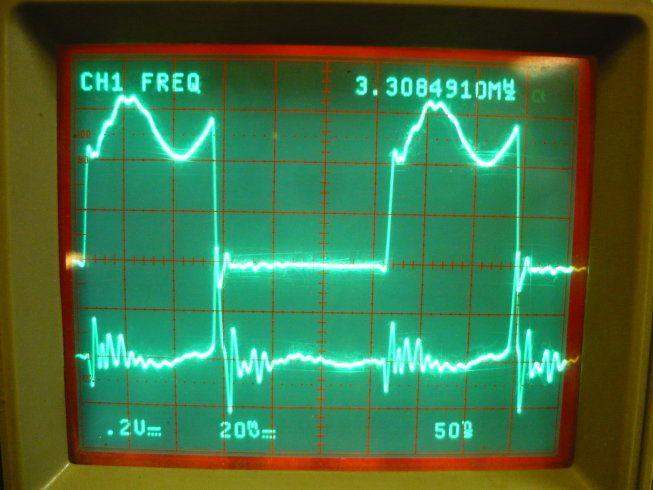

Figura 1: Ausência de capacitor de bypass

Isso parece com algum sinal digital? Isso é o que você tem sem capacitores de bypass.

Por favor atente ao fato que a frequência principal de operação é irrelevante. O problema são as bordas de subida e descida das saídas. Então sistemas com o clock 1Hz, 20kHz ou 50MHz necessitam das mesmas considerações. O uso das frequências nos exemplos abaixo foi escolhida apenas para tornar fácil a visualização no osciloscópio.

Deve-se destacar que projetos com alta frequência irão falhar mais rápido porque o número de transições é significamente maior que em projetos de baixa frequência. No entanto, isto não significa que projetos de baixa frequência são imunes. Longe disso, eles falham tão facilmente quanto Murphy nos ensinou. Há… você imaginou agora aquele seu pequeno microcontrolador rodando a 16Mhz ou talvez aquele controlador de LEDs, usado para o show de luzes?

Medindo correntes de surto

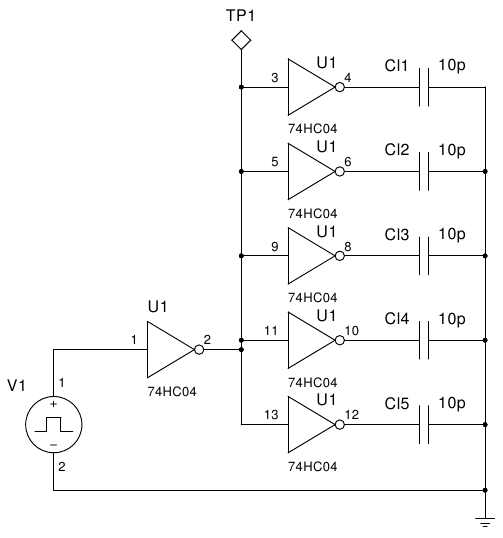

Para ver o que está acontecendo nós precisamos medir a corrente que flui. Um circuito de teste simples foi criado para ilustrar.

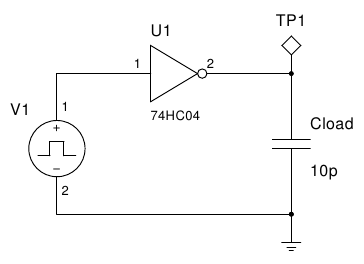

Figura 2: Circuito Inversor

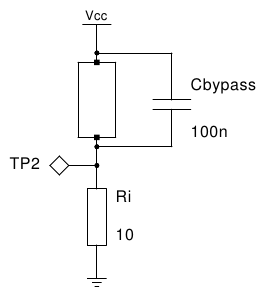

Figura 3: Medição de Corrente

Um gerador de pulso é conectado a um inversor 74HC04 e um capacitor de 10pF de capacitância é colocado como carga. A saída, TP1, é mostrada no traço superior do osciloscópio. A fonte de alimentação é conectada nos pinos 14 e 7 com um resistor de 10 ohm para o GND. A corrente de alimentação do 74HC04 é medida em TP2 e visualizada no traço inferior do osciloscópio. O capacitor de bypass é montado e desmontado como indicado no texto.

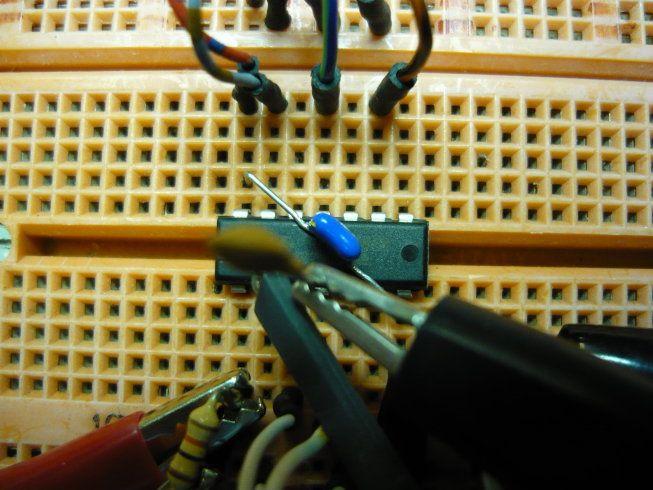

As pontas do osciloscópio usadas são do tipo 1:10, então todos os valores no eixo Y da imagem do osciloscópio devem ser multiplicados por um fator de 10. Todos os pinos não utilizados do 74HC04 são conectados ao GND. A configuração se parece com isso:

Figura 4: Montagem na breadboard

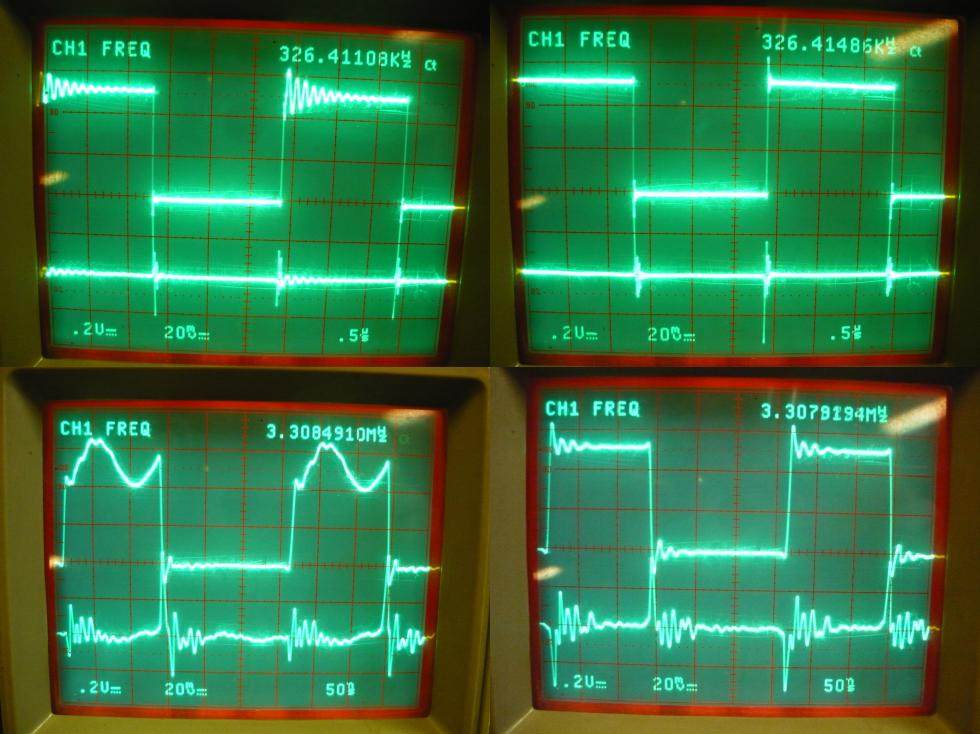

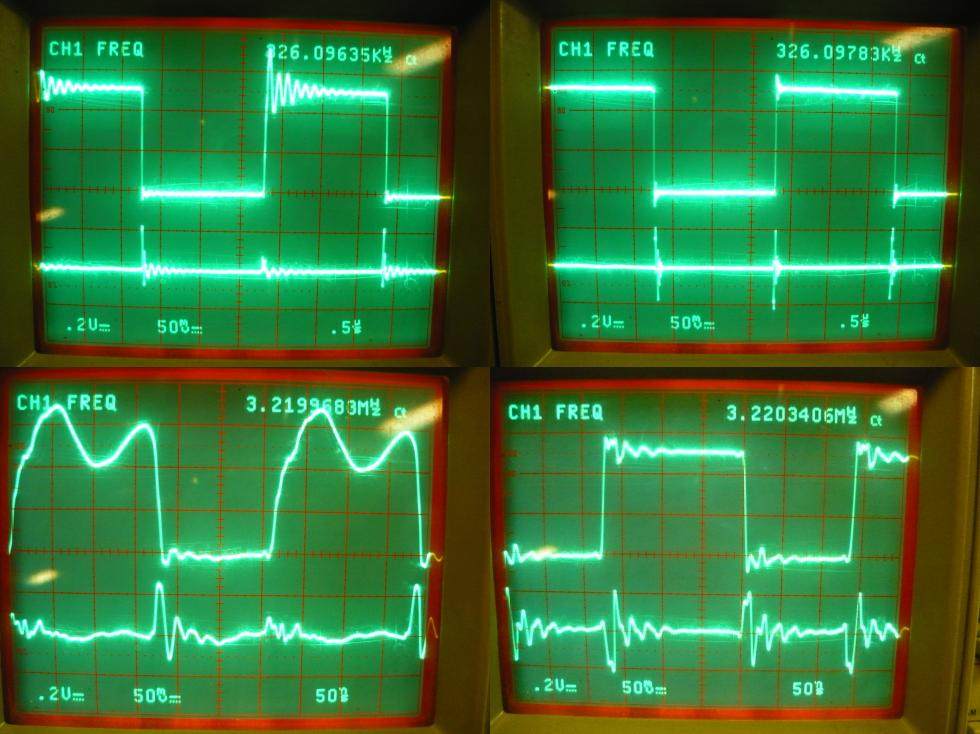

A Figura 5 ilustra o problema em baixas e altas frequências de entrada. As imagens da esquerda são sem os capacitores e os da direita são com os capacitores montados:

Figura 5: Saída e corrente sem (esquerda) e com (direita) capacitores de bypass

Algumas observações sobre a figura 5:

– A corrente medida é somente a que flui entrando e saindo através do GND da fonte de alimentação e o pino do 74HC04 e pelo capacitor de bypass, quando montado. Isto não representa toda a corrente que entra e sai da saída do inversor. É difícil medir correntes que fluem nos dois sentidos pelo Vcc e GND simultanetamente (com o osciloscópio no modo DC). No entanto, a corrente de GND é suficiente para ilustrar o problema do circuito.

– “Ruído” de alta frequência no nível alto da saída. Esta “oscilação” é de mais de 2V pico-a-pico e supera a fonte de alimentação (5V) significativamente. Adicionando os capacitores de bypass esta “oscilação” é reduzida a um nível virtualmente inexistente. Ainda existe este overshoot, mas ele é suprimido muito mais eficientemente.

– “Spikes” (picos) de corrente nas transições. Adicionar um capacitor de bypass reduz os spikes e torna-os simétricos nas transições de subida e descida. Os picos de corrente vão de -22 a +45mA sem o capacitor de bypass e de -32 a +36mA com o capacitor.

– A simetria da corrente nas imagens com o capacitor de bypass montado mostra que a energia é tando recuperada como armazenada. Isso é um fator muito importante.

– O ruído residual de altíssima frequência depende bastante da posição das ponteiras (não mostradas), o que indica que existem significativas antenas de RF no circuito (circuitos LC indesejados). O layout da breadboard (matriz de contatos) e a posição dos fios de conexão possuem impacto significativo na amplitude e frequência. Isso não pode ser eliminado mas pode ser bastante reduzido em um bom layout de PCI (placa de circuito impresso).

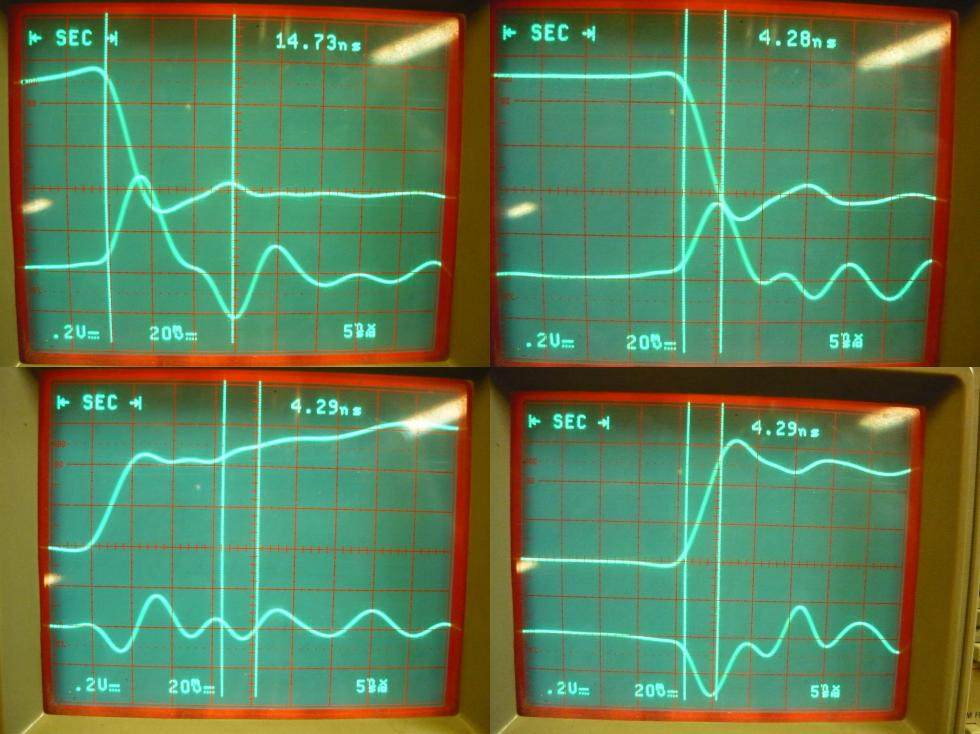

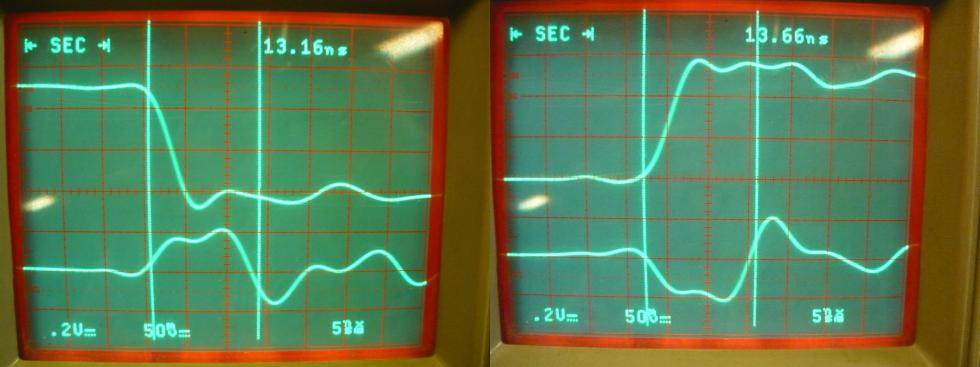

Olhando as transições em mais detalhes:

Figura 6: Detalhes da borda de saída e da corrente sem (esquerda) e com (direita) o capacitor de bypass

As correntes que fluem

O 74HC04 é um projeto de chip totalmente CMOS. Isso significa que a corrente estática drenada é próxima de zero. A corrente é desenhada nas transições de alto para baixo e de baixo para alto. Nas transições é que todas as cargas, parasitas ou não, precisam ser (des)carregadas. O circuito de teste da figura 2 possui um capacitor de 10pF como carga. O pino – e sua capacitância devem ser adicionadas, o que nós dá algo na ordem de 5pF+2pF. A ponteira do osciloscópio também possui sua capacitância, que adiciona outros 10pF. A capacitância total da carga na saída é, então, da ordem de 27pF.

Considerando somente essa capacitância de saída, nós estamos (des)carregando a carga com 5V a cada 4,3ns. Se assumirmos a medida da corrente constante (tornando os cálculos mais fáceis) nós podemos estimar a corrente através dos parâmetros acima, utilizando a equação da carga:

Q = I • t = C • U I = 5 • 27 • 10 -12 4.3 • 10 -9 ≅ 31.4mA

Isto significa que uma enorme corrente está fluindo em ambas direções para equilibrar a corrente em todas as direções. De onde vem todo este poder? Bom, da fonte de alimentação. Isso pode ser visto claramente na figura 6, onde temos que a corrente não é instantânea; ela acumula-se a um nível específico e depois cai de novo. Este comportamento indica claramente um elemento indutivo.

Isto pode ser visto melhor nas duas imagens da direita na figura 6 (com o capacitor de bypass), quando a corrente (o traço inferior) dá um pico no momento que a saída (traço superior) vai a zero. A corrente então cai, derrubando a saída com ela.

A corrente calculada comparada com as medições estão bem compatíveis, considerando que o nosso cálculo foi uma simples estimativa.

Então, para que o capacitor de bypass?

Dê outra olhada de perto nas duas imagens inferiores da figura 6. A esquerda não atinge o nível dos 5V na saída por algum tempo, enquanto a da direita não tem nenhum problema neste aspecto. Não há energia suficiente sem o capacitor de bypass para suportar a borda de subida e ela trava em 4V por algum tempo. Adicionar o capacitor de bypass supre o 74HC04 com potência instantânea neste período.

O capacitor de bypass é cerca de 4000 vezes maior que a capacitância da carga, o que significa que a queda de tensão esperada é cerca de 4000 vezes menor (na faixa de 1 a 2mV) para dar suporte à transição.

Quando a transição é no sentido contrário, como na parte superior das duas imagens da figura 6, então o capacitor de bypass funciona como um reservatório para receber a energia liberada. A capacitância da carga precisa ser descarregada e então a corrente quer fluir para o GND. No entanto, a energia não pode se mover facilmente para a fonte de alimentação principal e então o capacitor armazena-a temporariamente.

Fonte de alimentação sem potência

A fonte de alimentação principal não pode prover o chip lógico com toda a energia necessária por causa da indutância. Todo fio possui indutância (parasita) e isso dificulta as variações de corrente. A equação básica na eletrônica para indutância é:

U = L dI dt ⇒ dI = U • dt L

A partir desta equação pode ser visualizado que a mudança na corrente dI é inversamente proporcional a L (indutância). Em outras palavras, quando a indutância aumenta torna-se mais difícil alterar a corrente em determinado período de tempo, se todos os outros parâmetros permanecerem os mesmos. Além disso, uma mudança na corrente atual significa que há uma queda de tensão sobre a indutância. Um fio longo (ou uma trilha na PCI) tem indutância maior e, portanto, atua contra as mudanças rápidas de corrente provocando uma queda de tensão grande.

O capacitor de bypass é uma fonte local de energia. Ele precisa ser montado bem perto dos pinos de alimentação do CI, reduzindo assim a indutância entre o CI e o capacitor ao mínimo. Esta configuração desacopla a fonte principal do fornecimento de energia do chip.

Stress no inversor

Existem seis inversores no encapsulamento, então o circuito de teste foi modificado para consumir mais corrente:

Figura 7: Circuito de teste com carga adicional

Figura 8: Alta carga na saída e corrente sem (esquerda) e com (direita) o capacitor de bypass; note a mudança na escala da corrente

A corrente no pino de GND agora atinge pico de cerca de 70mA quando o capacitor de bypass não está instalado. Uma imagem simétrica é novamente visualizada com o capacitor de bypass instalado, mostrando +/-50mA, dependendo da borda, se subindo ou descendo.

Note que as transições, como mostrado na imagem inferior esquerda da figura 8, são significativamente mais irregulares. O 74HC04 simplesmente não possui energia para suportar a transição. Adicionando o capacitor de bypass (imagem da direita) a transição volta novamente a um nível aceitável.

Figura 9: Detalhe da borda alta com o capacitor de bypass; note a mudança na escala da corrente

O detalhe da borda revela uma alongado consumo de corrente, que é causado por uma demanda de energia muito mais alta. A carga no chip é seis vezes maior (o primeiro inversor tem uma carga 5 vezes ~5pF da capacitância dos inversores secundários).

Este foi só um exemplo com um CI de portas inversoras. Agora, extrapole a idéia para CIs lógicos complexos, que possuem muitas portas internamente com muitas transições. Existem muitas capacitâncias parasitas nas portas que precisam ser (des)carregados toda vez que uma entrada muda. Ou pense sobre microcontroladores, com milhares de portas lógicas lá dentro.

Aterramento

Apartir dessa explanação e visualização dos dados, deve ficar claro que o capacitor de bypass é um elemento importante com uma função bem definida. Ele armazena energia e libera quando necessário, além de recebê-la quando há excesso.

Esta fonte local está sempre sendo suprida pela fonte de alimentação principal através da conexão de Vcc. No entanto, o excesso de energia precisa ser devolvida para a fonte principal através da conexão de GND. Receber esta energia no capacitor de bypass eleva a tensão e, efetivamente, cria temporariamente uma ilha com um potencial diferente. Remover este desequilíbrio é muito importante e isto é feito através das conexões de GND.

Projeto de PCIs (Placas de Circuito Impresso) oferecem planos de aterramento que fazem conexões muito eficientes com a fonte principal. Um bom projeto de plano de GND é essencial para liberar a energia excessiva. Mas seja cauteloso, pois um simples plano de aterramento também pode induzir correntes parasitas (Foucault) e múltiplas conexões ao GND podem introduzir loops.

Sempre é uma boa idéia conversar com aquele experiente amigo projetista de PCIs. A maioria dos erros já foram cometidos e não há necessidade que sejam repetidos por nós ad infinitum.

Bertho Stultiens

Este artigo foi adaptado para o Eletronica.org a partir do original, em inglês, disponível em http://www.vagrearg.org/?p=decoupling, com autorização do autor.

Obra sob Attribution-ShareAlike 3.0 Unported (CC BY-SA 3.0)

Você tem a liberdade de:

- Compartilhar — copiar, distribuir e transmitir a obra.

- Remixar — criar obras derivadas.

- fazer uso comercial da obra

Sob as seguintes condições:

- Atribuição — Você deve creditar a obra da forma especificada pelo autor ou licenciante (mas não de maneira que sugira que estes concedem qualquer aval a você ou ao seu uso da obra).

- Compartilhamento pela mesma licença — Se você alterar, transformar ou criar em cima desta obra, você poderá distribuir a obra resultante apenas sob a mesma licença, ou sob uma licença similar à presente.